# COURSE GUIDE

# PHY 405 ELECTRONICS III

Course Team Dr. A. B. Adeloye & Dr. M. A. Chendo (Course

Developers) - UNILAG

Dr. Ajibola S. O. (Programme Leader) – NOUN

Dr. Adeniran A. O. (Course Reviewer)

NATIONAL OPEN UNIVERSITY OF NIGERIA

PHY 405 COURSE GUIDE

© 2023 by NOUN Press National Open University of Nigeria Headquarters University Village Plot 91, Cadastral Zone Nnamdi Azikiwe Expressway Jabi, Abuja

Lagos Office 14/16 Ahmadu Bello Way Victoria Island, Lagos

e-mail: centralinfo@nou.edu.ng

URL: www.nou.edu.ng

All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher.

Printed 2023

ISBN: 978-978-058-971-4

# MAIN COURSE

| CONTENTS |                                          |     |  |

|----------|------------------------------------------|-----|--|

| Unit 1   | Number System and Codes                  | 2   |  |

| Unit 2   | Fundamentals Of Boolean Algebra          |     |  |

|          | And Flip Flops                           | 28  |  |

| Unit 3   | Registers, Counters, Memory Circuits and |     |  |

|          | Analogue/Digital Converters              | 85  |  |

| Unit 4   | Electronic Instruments                   | 120 |  |

|          |                                          |     |  |

#### **DIGITAL ELECTRONICS**

#### **Course Introduction**

In the previous two previous courses: Network Analysis and Devices; and Electronics I, we dealt with analogue electronics in which the inputs and output are analogue (continuously varying) signals. In this course, we will be studying digital circuits where the signals are discrete.

The origin of digit was in the caves, thousands of years before writtenhistory, when man learnt to count on the fingers (digits). The basic number names, are therefore, known as digits. There are different numbering systems followed in digital electronics. In Unit 1 you will be introduced to some of the important number systems used. We will learn how to convert numbers from one system to another. We will discuss binary number and some mathematical operations using them.

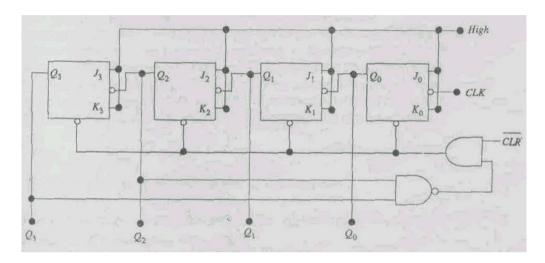

In Unit 2 we will introduce some of the circuits that are able to operate on binary numbers to perform a logical function. These circuits are called electronic gates. Also you will be familiarised with Boolean algebra which is used in digital systems. After having learned about different types of gates you will be introduced to the flip-flop, which can be built using gates.

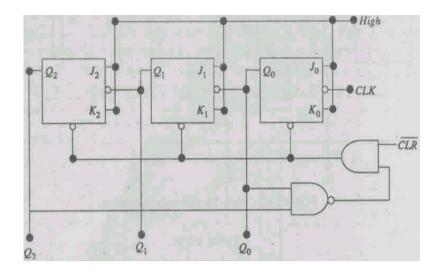

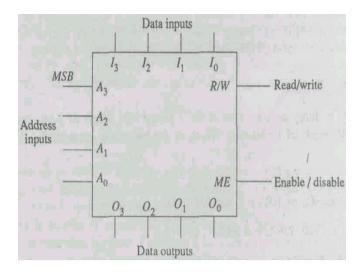

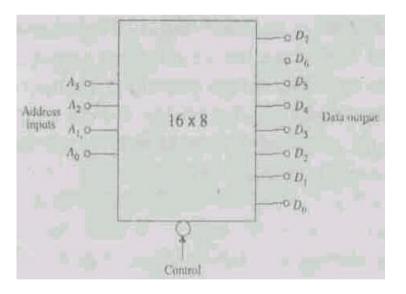

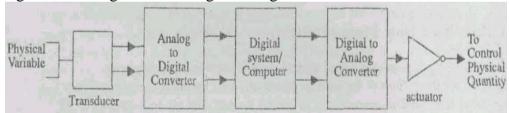

In Unit 3 we will study counters which are used for counting the digital pulses and registers which are used to store binary information. Many digital systems include some form of memory, where data can be held on a permanent or a temporary basis. There are different types of memories used in a digital system. We will learn about semiconductor memories in this Unit. Data from the physical world are usually analogue in form and continuous in time. The digital computer or processor operates with numbers and discontinuous data. To utilize the digital processor in the solution or control of physical problems it requires devices to sample the analogue data and code it in digital form or to perform reverse processing and decoding in conversion of processed information back to analogue form. Therefore, in Unit 3 we have discussed analogue to digital converter and their counterpart digital to analogue converter.

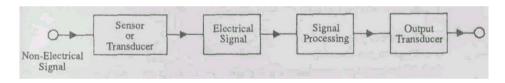

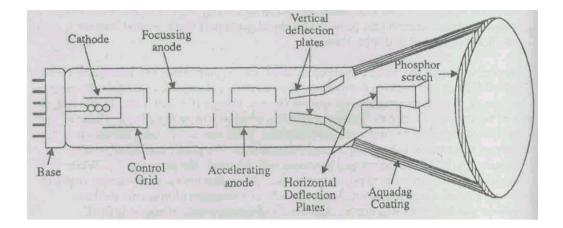

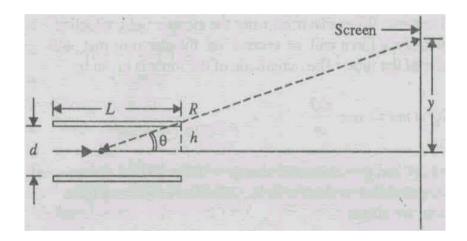

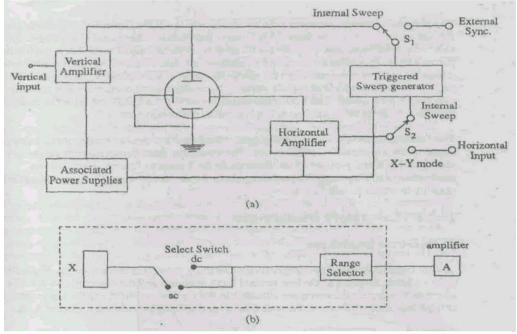

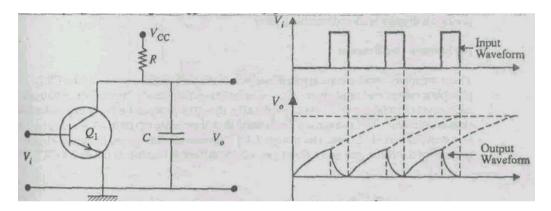

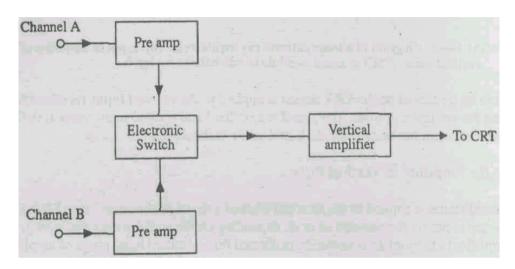

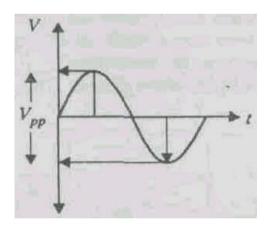

In Unit 4 we will come across many testing, measuring and indicating instruments like the CRO, electronic voltmeter, power meter etc. It would help the students to familiarise themselves with these instruments.

1

# **UNIT 1 NUMBER SYSTEM AND CODES Structure**

1.1 Introduction Objectives

1.2 Binary Number System

Binary to Decimal Conversion

Decimal to Binary Conversion

1.3 Octal Number System

Octal to Decimal Conversion

Decimal to Octal Conversion

Octal to Binary Conversion

Binary to Octal Conversion

1.4 Hexadecimal (Hex) Number System

Hex to Decimal Conversion

Decimal to Hex Conversion

Hex to Binary Conversion

Binary to Hex Conversion

Hex to Octal Conversion

Octal to Hex Conversion

1.5 Codes BCD Code ASCII Code

1.6 Binary Arithmetic

Addition

Subtraction

Multiplication and Division

- 1.7 Summary

- 1.8 Terminal Questions

- 1.9 Solutions and Answers

#### 1.1 INTRODUCTION

The aim of any number system is to deal with certain quantities, which can be measured, monitored, recorded, manipulated arithmetically, observed and utilised. Each quantity has to be represented by its value as efficiently and as accurately as is necessary for any application. The numerical value of a quantity can be basically expressed in either analogue (continuous) or digital (step by step) method of representation.

In analogue method, a quantity is expressed by another quantity which is proportional to the first. For example, the voltage output of an amplifier is measured by a voltmeter. The angular position of the needle of the voltmeter is proportional to the voltage output of the amplifier. Yet another example is of a thermometer. The height to which the mercury rises is proportional to the temperature. In both these examples, the value of voltage and temperature can be anywhere between zero and the maximum limit.

In digital method, the value of a quantity is expressed by some symbols, which are called digits, and not by a quantity which is proportional to the first. In a digital watch, the time, which changes continuously, is expressed by digits which do not change continuously. The hour-digits change every hour, and the minute-digits change every minute. But there is no measurement of time lapsed between two successive minute-digits. If we want to measure time more accurately then use can be made of watches which have second-digits as well. The second-digits change every second. The time passed between two seconds is not measured. If this is to be measured, we have to use sports watches where the time is measured up to 2 decimal places. Thus the time can be expressed by digits which change step by step (discrete). This step, which is an interval of time, in this example, can be made by us as small as necessary. Hence, the analogue, quantities like time can be represented as digital approximations (e.g. 10 hour 40 minutes, or more accurately 10 hour 39 minutes 50 seconds). As is clear from the examples above, the accuracy of the value of an analogue quantity generally depends upon the judgement of the observer.

Many number systems are being used in digital technology. Most common amongst them are decimal, binary, octal, and hexadecimal systems. We are most familiar with the decimal number system, because we use it everyday. In this unit we shall describe these number systems, the conversion of a number from one system to another, and finally binary arithmetic. This unit is intended to provide the first step in our understanding of digital electronics.

In the next unit you will be introduced to some of the gates, which are fundamental in digital electronics. There you will be familiarised with Boolean algebra which is a mathematical method used in the design of digital systems.

# **Objectives**

After studying this unit, you should be able to:

- write binary number and convert it into its decimal equivalent and a decimal number into its binary equivalent,

- explain octal number system, understand octal counting, convert an octal number into its decimal and binary equivalents and decimal and binary numbers into their octal equivalents,

- explain hexadecimal number system, understand hex counting, convert hex number into its decimal, binary and octal equivalents and decimal, binary and octal numbers into their hex equivalents,

- write BCD code and convert a decimal number into its equivalent BCD code and vice versa,

- understand ASCII code,

- learn addition, subtraction, multiplication and division using binary numbers.

#### 1.2 BINARY NUMBER SYSTEM

First let us consider the familiar decimal system. In this system there are ten distinct and different digits (0, 1, 2, 3, 4, 5, 6, 7, 8, and 9). For magnitudes greater than 9 the convention is to arrange digits in rows starting with the most significant on the left and concluding with the least significant on the right. The significance is determined by what is called the 'weighting' of a digit. Thus arises the concept of 'tens', 'hundreds', 'thousands', etc. For example  $3458 = (3 \times 10^3) + (4 \times 10^2) + (5 \times 10^1) + (8 \times 10^0)$ . Each digit is one of the symbols 0 to 9 and is multiplied by a power of ten, depending upon the position of the digit. Thus, decimal numbers are said to have a base of ten and the multiplying powers  $10^0$ ,  $10^1$ ,  $10^2$ ,  $10^3$ , etc. are called 'weight' or 'positional values'.

In the binary number system (base of 2), there are only two digits: 0 and 1 and the place values are  $2^{\circ}$ ,  $2^{1}$ ,  $2^{2}$ ,  $2^{3}$  etc. Binary digits are abbreviated as bits. For example 1101 is a binary number of 4 bits (i.e., it is a binary number containing four binary digits.)

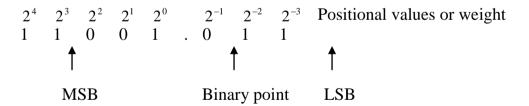

A binary number may have any number of bits. Consider the number 11001.011. Note the binary point (counterpart of decimal point in decimal number system) in this number. The bit on the extreme right is called least significant bit (LSB) and the bit on the extreme left is called most significant bit (MSB). Each bit has its positional value as shown in Fig. 1.1.

Fig. 1.1 Binary number: showing positional values (weight) of each bit

The bits on the left of the binary point are positive powers of 2 and bits on the right of binary point are negative powers of 2. The decimal equivalent of this number is found by summing the products of each bit and its positional value as follows:

$$\begin{split} I1001.011_2 &= (1\times 2^4) + (1\times 2^3) + (0\times 2^2) + (0\times 2') + (1\times 2^0) + (0\times^{-1}) + \\ (1\times 2^{-2}) + (1\times 2^{-3}) &= 16 + 8 + 0 + 0 + 1 + 0 + 0.250 + 0.125 = 25.375_{10}. \end{split}$$

Note that to avoid confusion the subscripts 2 and 10 are written with the numbers to indicate the base of the appropriate number system in which the number is expressed.

Any number can be expressed in binary form in the usual way as shown in Table 1.1

**Table 1.1 Counting in Binary System**

| 23 | 22 | 21 | <b>2</b> ° | Binary | Decimal |

|----|----|----|------------|--------|---------|

|    |    |    |            | Number | Number  |

| 0  | 0  | 0  | 0          | 0000   | 0       |

| 0  | 0  | 0  | 1          | 0001   | 1       |

| 0  | 0  | 1  | 0          | 0010   | 2       |

| 0  | 0  | 1  | 1          | 0011   | 3       |

| 0  | 1  | 0  | 0          | 0100   | 4       |

| 0  | 1  | 0  | I          | 0101   | 5       |

| 0  | 1  | I  | 0          | 0110   | 6       |

| 0  | 1  | I  | 1          | 0111   | 7       |

| 1  | 0  | 0  | 0          | 1000   | 8       |

| 1  | 0  | 0  | 1          | 1001   | 9       |

| 1  | 0  | 1  | 0          | 1010   | 10      |

| 1  | 0  | 1  | 1          | 1011   | 11      |

| 1  | 1  | 0  | 0          | 1100   | 12      |

| 1  | 1  | 0  | 1          | 1101   | 13      |

| 1  | 1  | 1  | 0          | 1110   | 14      |

| 1  | 1  | 1  | 1          | 1111   | 15      |

From this Table, note that 4 binary digits are required to do counting up to  $15_{10}$ . Thus if the number of bits is n, then we can go up to  $2^n$  counts and the largest decimal number represented will be  $2^n - 1$ . For example, in the above case, n = 4. Therefore, the largest decimal number represented is  $2^4 - 1 = 15_{10}$ . To write the next higher number in Table 1.1, we need an additional column for the next power of the base, i.e.,  $2^4$ .

# **SAO 1**

What is the largest decimal number that can be represented using 10 bits?

The advantage of binary system is that it has made the job of designing the digital circuitry very easy because only two distinct states or levels of voltages have to be handled. For example, 'ON' state of a bulb may be represented by the bit '1' and 'OFF' state by '0'. In terms of voltages, 0 V or a 'LOW voltage may represent bit '0' and 5V or a 'HIGH' voltage may represent bit '1'. Actually, it is not necessary also to have precise voltages assigned to each bit. In analogue system the exact value of voltage is very important which makes the design of accurate analogue

circuitry very difficult. However, in digital systems exact value of voltage is not important because a voltage of 3.9 V means the same thing as a voltage of 4.4 V or 5 V. This aspect will be dealt with in Unit 3.

Let us now see how binary numbers can be converted into equivalent decimal form and vice-versa.

#### 1.2.1 Binary to Decimal Conversion

From the example discussed above it is clear that a binary number can be converted into its decimal equivalent by simply adding the weights of various positions in the binary number which have bit 1. For example, consider the conversion of 100011.101<sub>2</sub>.

1 0 0 0 1 1. 1 0 1

$$2^{5} + 0 + 0 + 0 + 2^{1} + 2^{0} + 2^{-1} + 0 + 2^{-3}$$

=  $32 + 2 + 1 + 0.5 + 0.125 = 35.625_{10}$

Let us take up another example of conversion of 11100111.0101<sub>3</sub>.

$$= 128 + 64 + 32 + 4 + 2 + 1 + 0.250 + 0.0625 = 231.3125_{10}.$$

Consider the following examples.

$$1111.00 = 15$$

$11110.0 = 30$

$111100.0 = 60$

From these examples it is clear that if the binary point is shifted towards the right side, then the value of the number is doubled.

Now consider the following examples.

$$111.100 = 7.5$$

$11.1100 = 3.75$

$1.11100 = 1.875$

From these examples it is clear that if the binary point is shifted towards the left side, then the value of the number is halved.

## SA<sub>0</sub>2

Convert 1011.101 into its decimal equivalent.

## 1.2.2 Decimal to Binary Conversion

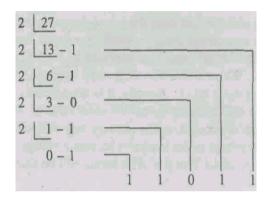

A decimal number is converted into its binary equivalent by its repeated divisions by 2. The division is continued till we get a quotient of 0. Then all the remainders are arranged sequentially with first remainder taking the position of LSB and the last one taking the position of MSB. Consider the conversion of 27 into its binary equivalent as follows.

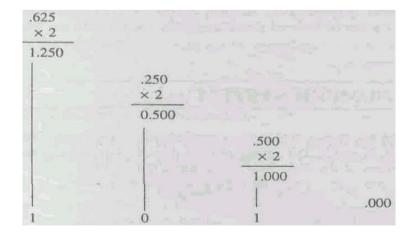

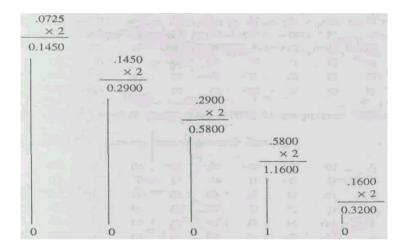

If the number also has some figures on the right of the decimal point, then this part of the number is to be treated separately. Multiply this part repeatedly by 2. After first multiplication by 2, either 1 or 0 will appear on the left of the decimal point. Keep this 1 or 0 separately and do not multiply it by 2 subsequently. This should be followed for every multiplication. Continue multiplication by 2 till you get all 0s after the decimal point or up to the level of the accuracy desired. This will be clear from the following example. Consider the conversion of  $27.625_{10}$  into its binary equivalent. We have already converted 27 into its binary equivalent, which is  $11011_2$ . Now for the conversion of 0.625, multiply it by 2 repeatedly as follows:

Thus  $27.625_{10} = 11011.101_2$ .

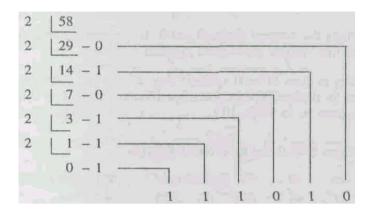

Let us try another example, conversion of 58.0725<sub>10</sub> into binary. Split this number in two parts, i.e. 58 and .0725 and convert them into binary separately as described above.

Now take up the conversion of .0725

Thus  $58.0725_{,0} = 111010.00010_2$

#### SAO3

What is the binary equivalent of  $37.75_{10}$ ?

Representing numbers in binary is very tedious since binary numbers often consist of a large chain of 0's and 1's. Imagine the length of the binary equivalent of a 10 digit decimal number! So, convenient shorthand forms for representing the binary numbers are developed such as octal system and hexadecimal system. With these number systems long strings of 0's and 1's can be reduced to a manageable form. Let us see what these systems are.

#### 10.3 OCTAL NUMBER SYSTEM

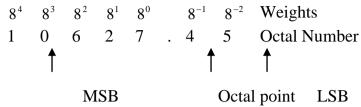

The octal number system has base-8, that is there are 8 digits in this system. These digits are 0, 1,2, 3, 4, 5, 6, and 7. The weight of each octal

digit is some power of 8 depending upon the position of the digit. This is explained in Fig. 1.2.

Fig. 1.2 Octal number: showing positional values (weight) of each digit

Octal number does not include the decimal digits 8 and 9. If any number includes decimal digits 8 and 9, then the number cannot be an octal number.

Now let us see how counting is done in octal system. You are familiar with the counting in decimal system. In decimal system there are 10 digits from 1 to 9 hence the counting in such system is done as in Table 1.2.

**Table 1.2: Counting in decimal system**

| 0 | 10 | 20 | 30 40 | 50   | 60 | 7 | 100 | 100 |       | 170 |

|---|----|----|-------|------|----|---|-----|-----|-------|-----|

| 1 | 11 | 21 | 31 41 | 51   | 61 | 7 | 101 | 111 |       |     |

| 2 | 12 | 22 | 32 42 | 2 52 | 62 | 7 | 102 | 112 |       |     |

| 3 | 13 | 23 | 33 43 | 53   | 63 | 7 | 103 | 113 |       |     |

| 4 | 14 | 24 | 34 44 | 1 54 | 64 | 7 | 104 | 114 |       |     |

| 5 | 15 | 25 | 35 45 | 5 55 | 65 | 7 | 105 | 115 |       |     |

| 6 | 16 | 26 | 36 46 | 5 56 | 66 | 7 | 106 | 116 |       |     |

| 7 | 17 | 27 | 37 47 | 57   | 67 | 7 | 107 | 117 |       |     |

| 8 | 18 | 28 | 38 48 | 58   | 68 | 7 | 108 | 118 |       |     |

| 9 | 19 | 29 | 39 49 | 59   | 69 | 7 | 109 | 119 | • • • | 179 |

In the same style, counting can be done in octal system as shown in Table 1.3

**Table 1.3: Counting in octal system**

| 0 | 10 | 20 30 | 40 | 50 | 60 | 70 | 100 |

|---|----|-------|----|----|----|----|-----|

| 1 | 11 | 21 31 | 41 | 51 | 61 | 71 | 101 |

| 2 | 12 | 22 32 | 42 | 52 | 62 | 72 | 102 |

| 3 | 13 | 23 33 | 43 | 53 | 63 | 73 | 103 |

| 4 | 14 | 24 34 | 44 | 54 | 64 | 74 | 104 |

| 5 | 15 | 25 35 | 45 | 55 | 65 | 75 | 105 |

| 6 | 16 | 26 36 | 46 | 56 | 66 | 76 | 106 |

| 7 | 17 | 27 37 | 47 | 57 | 67 | 77 | 107 |

In the octal counting, if n is the number of digits then the total number of counts is  $8^n$ . The largest decimal number represented by an octal number having n digits is  $8^n - 1$ . Thus with n = 4, the total number of counts is  $8^4 = 4096$  and the largest decimal number represented is  $4096 - 1 = 4095_{10}$ .

## SAQ4

Can the number 128.96 be an octal number?

#### **SAO 5**

What is the largest decimal number that can be represented by a three digit octal number?

#### 1.3.1 Octal to Decimal Conversion

As has been done in the case of binary numbers, an octal number can be converted into its decimal equivalent by multiplying the octal digit by its positional value. For example,

$$126.25_8 = (1 \times 8^3) + (2 \times 8^1) + (6 \times 8^0) + (2 \times 8^{-1}) + (5 \times 8^{-2})$$

= 64 + 16 + 6 + 0.25 + 0.078

= 86.328<sub>10</sub>

Let us convert 36.48 into decimal number.

$$36.4_8 = 3 \times 8^1 + 6 \times 8^\circ + 4 \times 8^{-1}$$

=  $24 + 6 + 0.5$

=  $30.5_{10}$

#### **S4Q6**

What is the decimal equivalent of  $37.2_8$ ?

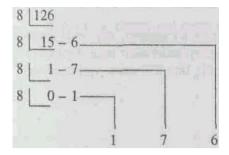

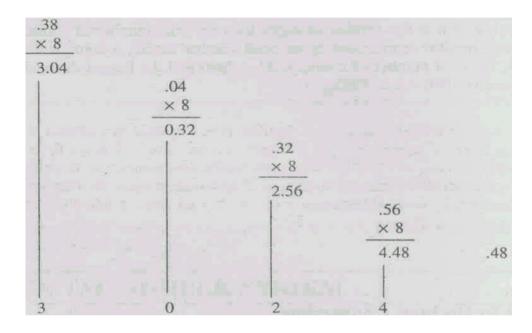

#### **1.3.2** Decimal to Octal Conversion

A decimal number can be converted by repeated division by 8 into the equivalent octal number. This method is similar to that adopted in decimal to binary conversion. If the decimal number has some digits on the right of the decimal point, then this part of the number is converted into its octal equivalent by repeatedly multiplying it by 8. The process is same as has been followed in the binary number system. Consider the conversion of 126.38<sub>10</sub> into its decimal equivalent. Split it into two parts, that is 126 and .38

Now the conversion of .38 is as follows:

Thus  $126.38_{10} = 176.3024_8$

#### **SAO 7**

What is the octal equivalent of  $15.250_{10}$ ?

# 1.3.3 Octal to Binary Conversion

In the octal number system the highest octal digit, i.e., 7 can be expressed as a 3-bit binary number. Therefore, all the octal digits have to be represented by a 3-bit binary number. The binary equivalent of each octal digit is shown in Table 1.4. The main advantage of the octal number system is the easiness with which any octal number can be converted into its binary equivalent.

Table 1.4: Binary equivalent of each octal digit

| Octal digit | 3-bit binary equivalent |

|-------------|-------------------------|

| 0           | 000                     |

| 1           | 001                     |

| 2           | 010                     |

| 3           | 011                     |

| 4 | 100 |

|---|-----|

| 5 | 101 |

| 6 | 110 |

| 7 | 111 |

Using this conversion of octal digit into 3-bit binary number, any octal number can be converted into its binary equivalent by simply replacing each octal digit by a 3-bit binary number. For example, conversion of 567<sub>8</sub> into its binary equivalent is:

$$567_8 = 101 \ 110 \ 111$$

$$= 101110111_2$$

Thus  $567_8 = 101110111_2$

## Another example:

Conversion of 672.278 into its binary equivalent.

$672.27_8 = 110\ 111\ 010.010\ 111$

= 110111010.010111

#### **SAO 8**

Represent 10027.128 in binary number.

#### **1.3.4** Binary to Octal Conversion

A binary number can be converted into its octal equivalent by first making groups of 3-bits starting from the LSB side. If the MSB side does not have 3 bits, then add 0s to make the last group of 3 bits. Then by replacing each group of 3 bits by its octal equivalent, a binary number can be converted into its binary equivalent. For example, consider the conversion of 1100011001<sub>2</sub> into its octal equivalent as follows:

$$1100011001_2 = 1\ 100\ 011\ 001$$

$$= 001\ 100\ 011\ 001$$

[As the MSB side does not have 3 bits, we have added two 0's to make the last group of 3 bits]

$$= 1\ 4\ 3\ 1$$

Thus  $1100011001_2 = 1431_8$

[As the MSB side does not have 3 bits, we have added two 0's to make the last group of 3 bits]

#### **SAO 9**

What is the octal equivalent of  $10010_2$ ?

#### 1.4 HEXADECIMAL NUMBER SYSTEM

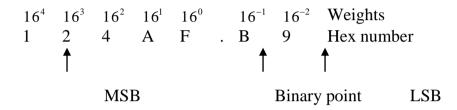

The hexadecimal number system has base-16, that is it has 16 digits (Hexadecimal means '16'). These digits are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F The digits A, B, C, D, E, and F have equivalent decimal values 10, 11, 12, 13, 14, and 15 respectively. Each Hex (hexadecimal is popularly known as hex) digit in a hex number has a positional value that is some power of 16 depending upon its position in the number. This is illustrated in Fig. 1.3.

Fig. 1.3: Hexadecimal number: showing positional values (weight) of each digit

The relationship of hex digits with decimal and binary numbers is given in Table 1.5. Note that to represent the largest hex digit we require four binary bits. Therefore, the binary equivalent of all the hex digits have to be written in 4-bit numbers.

| Table 1.5: Binar | y and Decimal | equivalent of | each Hex | Digit |

|------------------|---------------|---------------|----------|-------|

|------------------|---------------|---------------|----------|-------|

| Hex digit | <b>Decimal equivalent</b> | 4-bit Binary |

|-----------|---------------------------|--------------|

| 0         | 0                         | 0000         |

| 1         | 1                         | 0001         |

| 2         | 2                         | 0010         |

| 3         | 3                         | 0011         |

| 4         | 4                         | 0100         |

| 5         | 5                         | 0101         |

| 6         | 6                         | 0110         |

| 7         | 7                         | 0111         |

| 8         | 8                         | 1000         |

| 9         | 9                         | 1001         |

| A         | 10                        | 1010         |

| В         | 11                        | 1011         |

| С         | 12                        | 1100         |

| D         | 13                        | 1101         |

| Е         | 14                        | 1110         |

| F         | 15                        | 1111         |

While doing counting in hex number system if n is the number of hex digits then counting can be done up to  $16^n$  counts and the largest decimal number represented by a hex number is  $16^n - 1$ . The hex counting is shown in Table 1.6.

**Table 1.6: Counting in Hexadecimal system**

| 0 | 10 | 20 | 10 | 40 |       | 90 | A0 | B0 | C0         | D0 | E0 | F0 | 100 |

|---|----|----|----|----|-------|----|----|----|------------|----|----|----|-----|

| 1 | 11 | 21 | 31 | 41 |       | 91 | Al | B1 | <b>C</b> 1 | D1 | E1 | F1 |     |

| 2 | 12 | 22 | 32 | 42 |       | 92 | A2 | B2 | C2         | D2 | E2 | F2 |     |

| 3 | 13 | 23 | 33 | 43 | • • • | 93 | A3 | B3 | C3         | D3 | E3 | F3 |     |

| : | :  | :  | :  | :  | :     | :  | :  | :  | :          | :  | :  | :  |     |

| 9 | 19 | 29 | 39 | 49 |       | 99 | A9 | B9 | <b>C</b> 9 | D9 | E9 | F9 |     |

| A | 1A | 2A | 3A | 4A |       | 9A | AA | BA | CA         | DA | EA | FA |     |

| В | IB | 2B | 3B | 4B |       | 9B | AB | BB | CB         | DB | EB | FB |     |

| C | 1C | 2C | 3C | 4C |       | 9C | AC | BC | CC         | DC | EC | FC |     |

| D | ID | 2D | 3D | 4D |       | 9D | AD | BD | CD         | DD | ED | FD |     |

| E | ΙE | 2E | 3E | 4E |       | 9E | AE | BE | CE         | DE | EE | FE |     |

| F | IF | 2F | 3F | 4F |       | 9F | AF | BF | CF         | DF | EF | FF |     |

#### **SAQ 10**

What is the number next to  $835F_{16}$ ?

#### **SAQ 11**

What octal number represented by a 3-digit hex number?

## 1.4.1 Hex to Decimal Conversion

Hex to decimal conversion is done in the same way as in the cases of binary and octal to decimal conversions. A hex number is converted into its equivalent decimal number by summing the products of the weights of each digit and their values. This is clear from the example of conversion of 514.AF<sub>16</sub> into its decimal equivalent.

$$514.AF_{16} = 5 \times 16^{2} + 1 \times 16^{1} + 4 \times 16^{0} + 10 \times 16^{-1} + 15 \times 16^{-2}$$

$$= 1280 + 16 + 4 + 0.625 + 0.0586$$

$$= 1300.6836_{10}$$

#### **Another example:**

3BE.1A<sub>16</sub> =

$$3 \times 16^2 + 11 \times 16^1 + 14 \times 16^0 + 1 \times 16^{-1} + 10 \times 16^{-2}$$

=  $768 + 176 + 14 + 0.0625 + 0.0391$

=  $958.1016_{10}$

#### **SAO 12**

What is decimal equivalent of 1BE2<sub>16</sub>?

## 1.4.2 Decimal to Hex Conversion

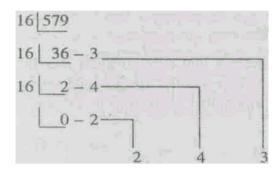

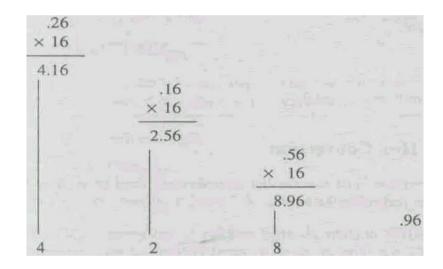

A decimal number is converted into hex number in the same way as a decimal number is converted into its equivalent binary and octal numbers. The part of the number on the left of the decimal point is to be divided repeatedly by 16 and the part on the right of the decimal point is to be repeatedly multiplied by 16. This will be clear from the examples of conversion of 579.26<sub>10</sub> into hex equivalent. Split the number into two parts 579 and .26.

Thus  $579_{10} = 243_{16}$ .

Now .26 is converted into hex number as follows:

Thus  $579.26_{IO} = 243.428_{16}$ .

# **SAQ 13**

What is the hex equivalent of  $37_{10}$ ?

## **1.4.3** Hex to Binary Conversion

As in octal number system, a hex number is converted into its binary equivalent by replacing each hex digit by its equivalent 4-bit binary number. This is clear from the following example:

$$BA6_{16} = B A 6$$

$$= 1011 1010 0110$$

$$= 1011101001102$$

## **SAO 14**

What is the binary equivalent of 6F10<sub>16</sub>?

#### 1.4.4 Binary to Hex Conversion

By a process that is the reverse of the process described in section 1.4.4 above, a binary number can be converted into its hex equivalent. Starting from the LSB side, group the binary number bits into groups of four bits. If towards the MSB side, the number of bits is less than four then add zeros on the left of the MSB so that the group of four is complete. Replace each group by its equivalent hex digit. This is clear from the following example:

$$1001101110_2 = 0010$$

0110 1110

= 2 6 E

=  $26E_{16}$

#### **SAQ 15**

What is the hex equivalent of 110010101001111<sub>2</sub>?

## 1.4.5 Hex to Octal Conversion

Each digit of the hex number is first converted into its equivalent four bit binary number. Then the bits of the equivalent binary number are grouped into groups of three bits. Then each group is replaced by its equivalent octal digit to get the octal number. For example,

#### **SAQ 16**

What is the octal equivalent of  $5A9_{16}$ ?

#### 1.4.6 Octal to Hex Conversion

For octal to hex conversion, just reverse the process described in section 1.4.6 above. This is clear from the following example:

$$5457_8 = 101$$

100 101 111

= 1011 0010 1111

$$= B 2 F_{16}$$

This method can also be applied to hex to decimal and decimal to hex conversions. For example consider the conversion of  $3C_{I6}$  into its decimal equivalent:

$$3C_{16} = 0011$$

1100

= 111 100<sub>2</sub>

Check the conversion.

$$3C_{16} = 3 \times 16^{1} + C \times 16^{0}$$

$$= 3 \times 16^{1} + 12 \times 16^{0}$$

$$= 48 + 12$$

$$= 60_{10}$$

$$111100_{2} = 2^{s} + 2^{4} + 2^{3} + 2^{2}$$

$$= 32 + 16 + 8 + 4$$

# Thus $3C_{16} = 111100_2 = 60_{10}$

#### **SAO 17**

What is the hex equivalent of 327<sub>8</sub>?

#### 1.5 CODES

So far you have learnt about binary, octal and hexadecimal number system. For any number system with a base B and digits  $N_0$  (LSB),  $N_1$ ,  $N_2$ , .....  $N_m$  (MSB), the decimal equivalent  $N_{10}$  is given by

$$N_{10} = N_m \times B^m + ... + N_3 \times B^3 + N_2 \times B^2 + N_1 \times B^1 + N_0 \times B^0 N_3 \times B^3$$

(1.1)

You have also observed that a number in any system can be written in the binary form. A number code is a relationship between the binary digits and the number represented. Thus, all number systems are codes and the decimal equivalent is given by Eq, (1.1). But there are other relationships or codes that relate decimal numbers and groups of binary digits that do not obey Eq. (1.1) These relationships are called codes. We will now discuss some of the important codes used in digital work.

#### 10.5.1 BCD Code

In BCD (BCD stands for binary coded decimal) code, each digit of a decimal number is converted into its four bit binary equivalent. The largest decimal digit is 9; therefore the largest binary equivalent is 1001. This is illustrated as follows:

$$951_{10} = 1001 \ 0101 \ 0001$$

$$= 100101010001_{BCD}$$

Remember that the conversion of a decimal number into its binary equivalent and BCD equivalent leads to two different numbers. For example:

$$158_{10} = 0001 \quad 0101 \quad 1000$$

$$= 10I011000_{BCD}$$

$158_{10} = 10011110_2$  (obtained by repeated division method).

Thus we see that it is quite easy to convert from decimal to BCD and from BCD to decimal. It is much easier to convert from BCD to decimal than from straight binary to decimal, because we only have to count up to 9 in binary to do so. However, it takes more bits to represent a number in BCD than in binary.

A BCD number is converted into its decimal equivalent by the reverse process. For example:

$$10101011100IO_{BCD} = 0001 0101 0111 0010$$

$$= 1 5 7 2$$

$$= 1572_{10}$$

Although the main function of a computer is to perform arithmetic operations, it also processes messages and information in a language that uses letters of the alphabet (e.g. English) and data of other kinds. Computers operate by coding letters of the alphabet, other symbols, and data into binary form. The code used for this purpose is the ASCII code, which you will study now.

#### 1.5.2 ASCII Code

The word ASCII is an acronym of American Standard Code for Information Interchange. This is the alphanumeric code most widely used in computers. The alphanumeric code is one that represents

alphabets, numerical numbers, punctuation marks and other special characters recognised by a computer. The ASCII code is a 7-bit code representing 26 English alphabets, 0 through 9 digits, punctuation marks, etc. A 7-bit code has  $2^7 = 128$  possible code groups which are quite sufficient. A partial ASCII code listing is shown in Table 10.6.

Table 1.6: Some of the ASCII codes for numbers, alphabets and other common symbols

|     |     | $A_6A_5A_4$ |     |     |     | $A_3A_2A_1$ |

|-----|-----|-------------|-----|-----|-----|-------------|

| 010 | 011 | 100         | 101 | 110 | 111 |             |

| SP  | 0   | @           | р   |     | р   | 0000        |

| 1   | 1   | A           | Q   | a   | q   | 0001        |

| "   | 2   | В           | R   | b   | r   | 0010        |

| '#  | 3   | C           | S   | c   | S   | 0011        |

| \$  | 4   | D           | T   | d   | t   | 0100        |

| %   | 5   | E           | U   | e   | u   | 0101        |

| &   | 6   | F           | V   | f   | V   | 0110        |

| 1   | 7   | G           | W   | g   | W   | 0111        |

| - ( | 8   | Н           | X   | h   | X   | 1000        |

| )   | 9   | I           | Y   | i   | y   | 1001        |

| *   |     | J           | Z   | j   | Z   | 1010        |

| +   | ;   | K           |     | k   |     | 1011        |

| ,   | <   | L           |     | 1   |     | iioo        |

| -   | =   | M           |     | m   |     | 1!01        |

|     | >   | N           | -   | n   |     | 1110        |

| /   | 9   | O           |     | O   |     | 1111        |

The code is  $A_6A_5A_4A_3A_2A_1A_0$ . For example, A has  $A_6A_5A_4$  of 100 and an  $A_3A_2A_1A_0$  of 0001. Therefore, its ASCII code is

$100\ 0001 = A$

The ASCII code for a is 110 0001.

#### **SAQ 18**

What is the ASCII code of SHARM?

#### 1.6 BINARY ARITHMETIC

Digital computers can perform arithmetic operations using only binary numbers. We will learn how to add, subtract, multiply and divide binary numbers. We will first review this in the familiar decimal system and apply the same ideas to the binary system.

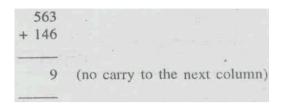

#### 1.6.1 Addition

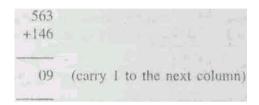

Let us recall the addition in decimal numbers. Suppose we want to add 563 and 146. We start adding the digits in the least significant column. We get,

Next, the digits of the second column are added and we get,

In this case 6 + 4 gives 0, with a carry 1 to the next column. Then the digits of the last column and the 'carry' from the previous column are added. We get,

```

563

146

1 ...... carry from previous column

709 (no carry)

```

The addition of binary numbers can be carried out in a similar way by the column method. But before we do this, we need to discuss four simple cases. We known in the decimal number system, 3 + 6 = 9 symbolizes the combining of ... with ..... to get a total of ...... Let us now discuss the four simple cases.

- Case 1: When nothing is combined with nothing, we get nothing. The binary representation of this is 0 + 0 = 0.

- Case 2: When nothing is combined with ., we get . Using binary numbers to denote this gives 0 + 1 = 1.

- **Case 3:** Combining . with nothing gives. The binary equivalent of this is 1 + 0 = 1.

- Case 4: When we combine . with ., the result is .. Using binary numbers, we symbolize 1 + 1 = 10.

The last result is sometimes confusing because of our long time association with decimal numbers. But it is correct and makes sense because we are using binary numbers. Binary number 10 stands for.. and not for ....... (ten).

To summarize our results for binary addition,

$$0 + 0 = 0$$

$$0 + 1 = 1$$

$$1 + 0 = 1$$

$$1 + 1 = 10$$

To add large binary numbers, carry into higher-order columns as is done with decimal numbers. As an example, add 10 to 10 as follows

In the first column, 0 plus 0 is 0. In the second column, 1 plus 1 is 0, carry a 1. As another example, take 1+1+1. Add two of the 1's to get 10+1.

Adding again gives 11 as follows:

$$1 + 1 + 1 = 10 + 1 = 11$$

See another example:

Further examples are

In all digital networks or computers only two binary numbers are added at a time. To add more than two numbers, first two numbers are added,

then to their sum the third number is added, and so on. Therefore, we should not worry about the addition of more than two numbers. The computer can add numbers in a few microseconds or even less. You will see that the multiplication, division and subtractions are actually done by the computers by way of addition.

## **SAQ 19**

Add the following:

- (a) 1010 and 1101

- (b) 1011 and 1010

#### 1.6.2 Subtraction

Binary subtraction is done in the same way as in decimal system. Let us recall the decimal subtraction, for example.

| 111   | first column : | 1 - 1 = 0 |

|-------|----------------|-----------|

| - 101 | second column: | 1 - 0 = 1 |

| 010   | third column:  | 1 - 1 = 0 |

In this example, a 1 is borrowed from the ten's position giving 16 in the LSD. Then 16-9 = 7. Borrowing a 1 from the ten's position leaves 4 in place of 5. Then 4 - 4 = 0. In the same way the binary subtraction can be done.

To subtract binary numbers, we first need to discuss four simple cases.

| Case 1 | 0 - 0 = 0 |

|--------|-----------|

| Case 2 | 1 - 0 = 1 |

| Case 3 | 1 - 1 = 0 |

**Case 4**

$$10 - 1 = 1$$

The last result represents ... = . which makes sense. To subtract large binary numbers, subtract column by column, borrowing from the adjacent column when necessary. For example, in subtracting 101 from 111, we proceed as follows:

| 111   | first column:  | 1 - 1 = 0 |

|-------|----------------|-----------|

| - 101 | second column: | 1 - 0 = 1 |

| 010   | third column:  | 1 - 1 = 0 |

Here is another example: subtract 1010 from 1101.

| 1101<br>- 1010 | first column:<br>second column: | 1 - 0 = 1<br>10 (after borrow) - 1 = 1  |

|----------------|---------------------------------|-----------------------------------------|

|                | third column:<br>fourth column: | 0 (after borrow) $-1 = 0$<br>1 - 1 = 0. |

## **SAO 20**

Subtract binary 100011 from 110011.

# 1.6.3 Multiplication and Division

The multiplication of binary numbers is also done in the same manner as in decimal system. It is rather easier, because the multiplication table for binary has only four cases.

| Case 1 | $0 \times 0 = 0$ |

|--------|------------------|

| Case 2 | $0 \times 1 = 0$ |

| Case 3 | $1 \times 0 = 0$ |

| Case 4 | $1 \times 1 = 1$ |

For example, in multiplying 1101 by 1001, we proceed as follows:

In the beginning the first partial product is written. Subsequently, each partial product is written below the previous one by shifting one place towards the left relative to the previous place. However, the digital circuits or computers add only two binary numbers at a time. Therefore, to the sum of first two partial products is added the third partial product. To this sum is added the third partial product to give the final sum.

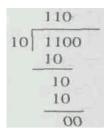

The process of dividing a binary number is once again the same as followed in the decimal system. To divide 1100 by 10, we proceed as follows.

#### **SAQ 21**

Multiply 10110 by 110.

#### 10.7 SUMMARY

There are mainly four number systems namely, binary, octal, decimal and hexadecimal, which have 2, 8, 10 and 16 digits respectively. But it is the ease in applications that decides which kind of number system should be defined and used. Every computer uses two or more of the above mentioned number systems simultaneously.

The binary number system has only two digits: 0 and 1. A binary digit is called bit. A binary number can be converted into its equivalent octal, decimal and hex numbers as described in the text. And also octal, decimal and hex numbers can be converted into equivalent binary numbers.

The octal number system has 8 digits: 0 through 7. An octal number can be converted into its equivalent binary, decimal and hex numbers and vice versa as described in the text.

The hex number system has 16 digits: 0 through 9, A (10) through F (15). As in the other systems, the hex numbers can be converted as described in the text into their binary, octal and, decimal equivalents and vice versa.

It is possible to arrange sets of binary digits to represent numbers, letters of the alphabet or other information by using a given code. Some of the important codes are the BCD and the ASCII codes.

In the BCD code, each decimal digit is replaced by its 4-bit binary equivalent. The conversion of BCD code into its decimal equivalent and vice versa is quite easy. Therefore, it is quite often used in computers.

The ASCII code is the most widely used alphanumeric code. It is a 7-bit binary number and has  $2^7 = 128$  possible 7-bit binary numbers, which are quite sufficient to describe the capital and small letters of the alphabet, digits, punctuation marks, and other symbols.

The fundamental arithmetic of binary addition is contained in four rules:

1.

$$0 + 0 = 0$$

- $2. \quad 0 + 1 = 1$

- 3. 1 + 0 = 1

- 4. 1 + 1 = 0 but 1 must be carried over to next higher (more significant) bit.

The fundamental arithmetic of binary subtraction is contained in four rules:

- 1. 0-0=0

- 2. 0-1=1 and borrow 1 from the next more significant bit

- 3. 1-0=1

- 4. 1-1=0

The four rules for binary multiplication are:

- 1  $0 \times 0 = 0$

- $0 \times 1 = 0$

- $3 \qquad 1 \times 0 = 0$

- $4 1 \times 1 = 1$

## 1.8 TERMINAL QUESTIONS

- (1) In the binary sequence, what is number that follows 10111?

- (2) What is the largest decimal number that can be expressed by 6 bits?

- (3) Convert 11011011011010.1101<sub>2</sub> into its decimal equivalent.

- (4) Convert 372.125,0 into its binary equivalent.

- (5) Convert 89.875<sub>10</sub> into its binary equivalent.

- (6) What is the largest decimal number represented by a five digit octal number?

- (7) Convert 7777<sub>8</sub> into its decimal equivalent.

- (8) Convert 6789<sub>10</sub> into its octal equivalent.

- (9) Convert 23401<sub>g</sub> into its binary equivalent.

- (10) Convert 110011011100I010<sub>2</sub> into its octal equivalent.

- (11) Add the following binary numbers 1110001 and 1010101

- (12) Multiply 101.1 by 11.01

- (13) Divide 11011 by 100

#### 1.9 SOLUTIONS AND ANSWERS

## **SAQs**

- 1. Largest decimal number =  $2^n 1$ . With n = 10,  $2^{10} 1 = 1024 1 = 1023_{10}$

- 2. 11.625<sub>10</sub>

- 3. 100101.11

- 4. No. Octal numbers do not have digits 8 and 9

- 5. The largest decimal number is  $8^3 1 = 512 1 = 511_{10}$

- 6. 31.250<sub>10</sub>

- 7. 17.28

- 8. 0010000000I0111.001010<sub>2</sub>

- 9. 228

- 10. 8360<sub>16</sub>

- 11. Largest decimal number =  $16^3 1 = 4096 1 = 4095_{10}$ .

- 12.  $1BE2_{16} = 1 \times 16^3 + 11 \times 16^2 + 14 \times 16^1 + 2 \times 16^0 = 4096 + 2816 + 224 + 2$

- 13. 25<sub>16</sub>

- 14.  $6F10_{16} = 0110$  1111 0001  $0000 = 110111100010000_2$

- 15.  $1100101010101111_2 = 0110 \ 0101 \ 0100 \ 1111 = 654F_{16}$

- 16.  $5A9_{16} = 0101 \quad 1010 \quad 1001$ = 010 110 101 001 = 2651<sub>8</sub>

- 17.  $3278 = 011 \ 010 \ 111$ =  $01101 \ 0111$ =  $D7_{16}$

- 18. SHARM = 1010011 1001000 1000001 1010010 1001101

- 19. (a) 10111 (b) 10101

- 20. 10000

- 21. 10000100

# **TQs**

- (1)  $11000_2$

- (2)  $63_{I0}$

- (3) 1754.8125<sub>10</sub>

- (4) 101110100.001<sub>2</sub>

- (5) 1011001.111<sub>2</sub>

- (6) 32767<sub>10</sub>

- $(7) 4095_{10}$

- (8) 15205<sub>8</sub>

- (9) 100 111 00000001<sub>2</sub>

- (10)11001101110010102 001 100 110 111 = 001 010 1 4 6 7 1 2 = 1467128 =

- (11) 11000110

- (12) 10001.111

- (13) 110.11

## References

Floyd, T. L., & Patterson, R.T., (2018). Digital Fundamental (11th ed). Pearson.

Rabaey, J.M., Chandrakasan, A., & Nikolic, B. (2018), Digital Integrated Circuits: A Design Perspective (2nd ed.) Prentice Hall.

Brown, S., Vranesic, Z. (2018). Fundamental of Digital Logic with Verilog Design (3rd ed). McGraw Hill Education.

Rabaey, J.M., Chandrakasan, A., & Nikolic, B. (2018), Digital Integrated Circuits: A Design Perspective (2nd ed.) Prentice Hall.

Floyd, T. L., & Patterson, R.T., (2018). Digital Fundamental (11th ed). Pearson.

Tokheim, R. L., (2016), Digital Electronics: Principles and Applications (8th ed). McGraw-Hill Education.

Mano, M.M. & Kime, C.R., (2104). Digital Logic and Computer Design (5th ed). Pearson.

# UNIT 2 FUNDAMENTALS OF BOOLEAN ALGEBRA AND FLIP FLOPS

#### **Structure**

2.1 Introduction

Objectives

2.2 Logic Gates

**AND Gate**

OR Gate

**NOT Gate**

Combination of Logic Gates

2.3 Boolean Algebra

**Boolean Theorems**

Algebraic Method for Combinational Logic

Obtaining a Truth Table from a Boolean Expression

Obtaining a Boolean Expression from a Truth Table

**Exclusive-OR Gate**

**Exclusive-NOR Gate**

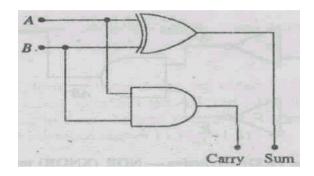

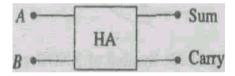

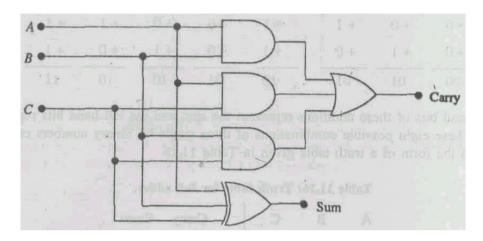

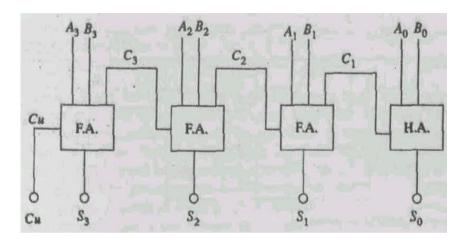

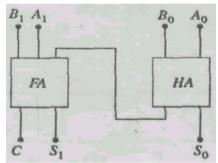

Addition of Two One Bit Binary Numbers (Half Adder)

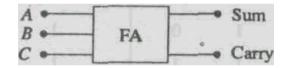

Addition of Three One Bit Binary Numbers (Full Adder)

Designing Circuits Using NAND Gates Only

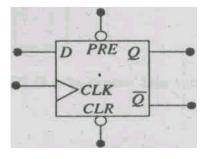

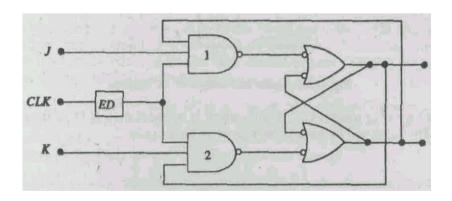

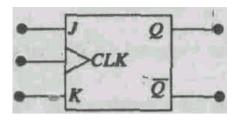

2.4 Flip-flops

RS flip-flop

Clocked RS Flip-flop

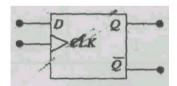

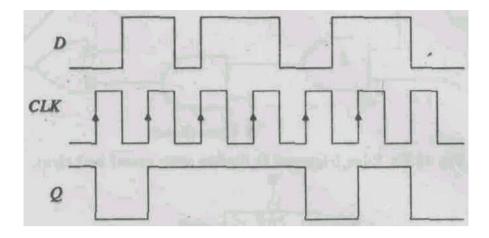

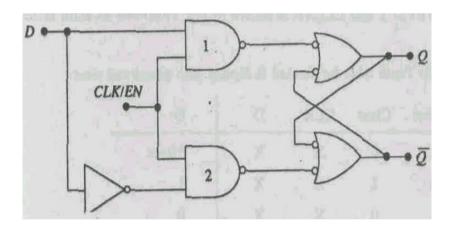

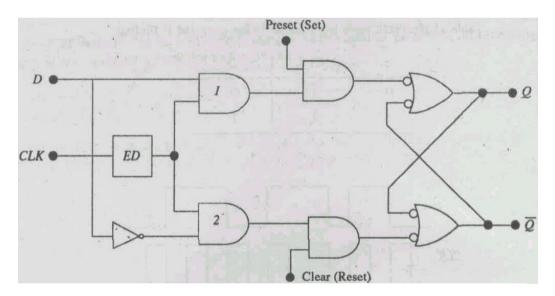

Clocked D Flip-flop

Clocked JK Flip-flop

- 2.5 Summary

- 2.6 Terminal Ouestions

- 2.7 Solutions and Answers

#### 2.1 INTRODUCTION

A digital circuit is designed for a desired application by a combination of several logic gates. This application involving several logic gates may be a simple or complex one. Different users may design digital circuits by using different combinations of logic gates for the same application. In selecting one of these digital circuits for that application, it is necessary to keep in mind that the chosen digital circuit should have a minimum number of logic gates. By seeing a digital circuit, it is not obvious that a circuit is minimal or certain gates may be removed from the circuit without changing its operation. Boolean algebra provides a means by which logic circuitry may be expressed symbolically, manipulated and reduced.

In this Unit we shall learn about three basic logic gates: AND, OR, NOT and their various combinations. All digital (logic) circuits operate in the binary mode, where all the inputs and outputs are predefined voltages representing binary digit either 1 or 0. It is this characteristics of the

logic circuits that enables us to use Boolean algebra for designing and analysing digital systems. This area of digital circuitry is known as combinational (or combinatorial) logic, where the relationship between the inputs and outputs can be precisely defined by the logic summarised in a truth table.

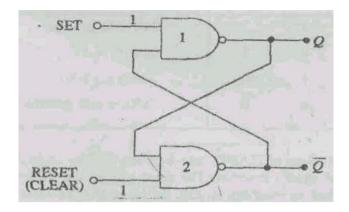

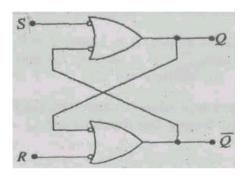

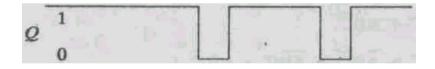

In the combinational logic circuit, there is no memory, i.e., the output of the digital circuit does not depend upon the occurrence of a previous event. But it is very essential for more advanced digital circuits meant for storing and manipulating information to have memory. The basic memory element is a flip-flop which is obtained by using NAND or NOR gates. In this Unit we shall learn about various kinds of flip-flops and their operation. This area of digital circuitry is known as sequential circuits.

#### **Objectives**

- After studying this unit, you should be able to

- describe the operation of AND, OR and NOT Gates and write their truth tables,

- describe the combination of gates and write the truth tables of NAND and NOR gates,

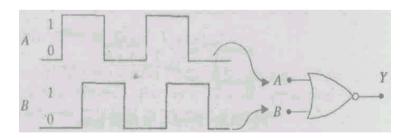

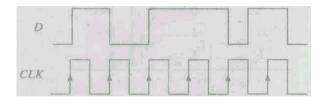

- explain as to how a timing diagram of the output of all the logic circuits is obtained,

- explain how the operation of three basic logic gates leads us to various theorems or rules used in Boolean algebra,

- write Boolean theorems and use algebraic method for combinational logic,

- obtain a truth table from a give Boolean expression,

- describe the operation of exclusive-OR and exclusive-NOR gates,

- design a half adder and describe its operation,

- design a full adder and describe its operation,

- design logic circuits using only NAND gates,

- describe the construction and explain the operation of the RS flipflop,

- describe the construction and explain the operation of clocked RS flip-flop, D flip-flop, and JK flip-flop, .

- obtain the timing diagrams of the outputs of flip-flops.

#### 2.2 LOGIC GATES

A logic gate is a digital circuit which has logical relationship between input and output voltages. There are three basic gates: AND, OR and NOT (also called inverter) gates. We shall now learn these gates one by one.

#### **2.2.1 AND** Gate

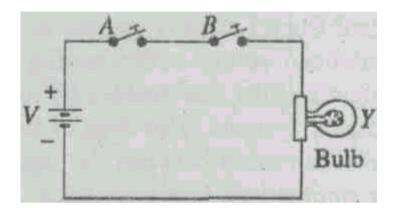

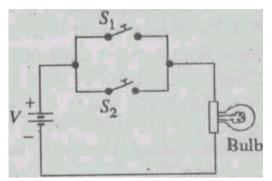

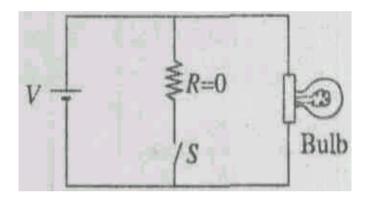

The AND gate can be understood by the circuit given in Fig. 2.1. In this circuit switch (s) is input and the bulb is output. Let us assign 0 to the event when the switch is open and 1 to the event when the switch is closed. Similarly when the bulb does not glow we call it 0 and when the bulb glows we call it 1. With both the switches (A and B) off, the bulb (Y) does not glow.

Fig. 2.1 AND gate using switches

With one of the switches off and another switch on, once again the bulb (Y) does not glow. However, with both the switches (A and B) on, the bulb (Y) glows. Thus there are four events which can be summarised in the form of a table which is called the truth table of this circuit. This is given in Table 2.1. The switches A and B, which control the input voltage are usually called the input of the truth table and Y as the output.

Table 2.1: Truth Table of AND Gate

| <b>Inputs</b> |   | Output |

|---------------|---|--------|

| A             | В | Y      |

| 0             | 0 | 0      |

| 0             | 1 | 0      |

| 1             | 0 | 0      |

| 1             | 1 | 1      |

#### Fundamentals of Boolean Algebra and Flip flops

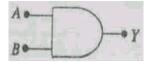

From this table it is clear that the bulb glows (1) only when both the switches (A and B) are on (1). Stated in a different way, the output is 1 when both the inputs A and B are 1. This state of the circuit is distinct from the other three states. This circuit is known as the AND gate. The symbol of AND gate is given in Fig. 2.2. It is clear from the Fig. 2.1 that if the circuit has any number of switches in series, then the output will be 1 if and only if all inputs are 1. Now for all times to come, you must remember that for an AND gate the output is 1 if and only if all the inputs are 1.

Fig. 2.2 Symbol of AND gate

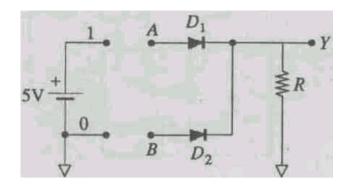

Electronically the AND gate can be realised by using two pn junction diodes as shown in the circuit of Fig. 2.3. The resistor *R* is used to control the current passing through the diodes. As slated above, a 0 bit is assigned 0V and a 1 bit is assigned 5V. However, such accurate values of voltage will not always be available at the output in electronic circuits. Therefore, a 0 bit is assigned a voltage range of 0 to 0.8V and a 1 bit is assigned to a voltage range of 2.8 to 5.0V. Quite often these voltage ranges are referred to a LOW and a HIGH respectively. The voltages greater than 0.8V and less than 2.8 V are indeterminate and hence not used.

Fig. 2.3 Realisation of AND Gate using diodes

In the circuit of Fig. 2.3 when the inputs A and B are 0, i.e. when they are connected to the 0V or ground terminal, both the diodes are forward biased with a voltage drop of 0.7V across each diode if the diodes are of Si or of 0.3V if the diodes are of Ge. Hence the output voltage is a LOW or a 0 bit. If the input A is 0 and B is 1 (i.e. 5V), the diode A is forward biased with 0.7V drop across it (assuming diode to be of Si) while the diode B is not biased (because both p and n sides of the diode are at the same voltage, 5V). Therefore the output voltage is 0.7V, i.e. a LOW or a 0 bit. Similarly, if the input A is 1 and input B is 0, the output is a 0. However, if both inputs are 1, i.e. connected to 5V, then both the sides of the diodes are at the same voltage and hence not conducting. Therefore, the output voltage is nothing but the battery voltage which is 5V, i.e. a HIGH or a 1 bit. These four cases satisfy the truth table of Table 2.1. For more input AND gate, the number of diodes may be more. The input output relationship of the AND gate is written as A.B = Y and is read as A AND B equal to Y.

## Example 2.1

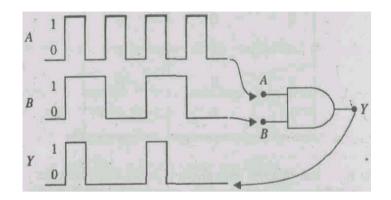

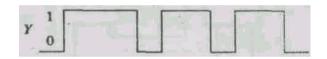

If the inputs A and B to the AND gate are as shown in Fig. 2.4, trace the output Y.

Fig. 2.4

#### **Solution**

Recall that the output of an AND gate is 1 when all the inputs are 1. If any of the inputs is 0, then the output is 0. With this understanding, the output comes out to be as shown in the trace for Y.

## SAQ 1

Trace the output of an AND gate, if the inputs A and B are as shown in Fig. 2.5.

Fig. 2.5

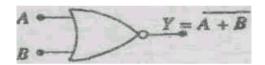

# **2.2.2 OR Gate**

The OR gate operation can be understood by the circuit of Fig. 2.4. If both the switches are off, (0), the bulb does not glow (0). If one of the switches is on (1) and other is off (0), the bulb glows (1). And if both the switches are on (1), then also the bulb glows (1). These events are summarised in the truth table given in Table 2.2.

Fig. 2.6 OR gate using switches

Table 2.2: Truth Table of OR Gate

| A | В | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

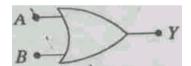

It is clear from the truth table that the output of an OR gate is 0 if both the inputs are 0 and the output is 1 if any one of the inputs or both the inputs are 1. If a larger number of switches are used in parallel in the circuit, then the bulb does not glow if all the switches are off, and the bulb glows if any one of the switches is on. The symbol of OR gate is given in Fig. 2.7. The OR gate operation is expressed as A + B = Y and is read as A + B = Y.

Fig. 2.7 Symbol of OR gate

Electronically OR gate can be realised by using two pn junction diodes as shown in the circuit of Fig. 2.8. If both the inputs are 0, that is connected to ground, then the diodes are not biased and hence no current flows through the diodes. The output is zero or a 0 bit. If the input to diode A is 0 and B is 1 (i.e. 5V), then the diode A is not -biased and thus does not conduct, but the diode B is forward biased with a 0.7V drop across it and 4.3V drop across the resistor. Thus the output is a HIGH or a 1 bit. Similarly, if the inputs to the diode A is 1 and diode B is 0, the output is 1. When the inputs to both the diodes A and B are 1, both the diodes are forward biased, the voltage drop across the resistor R continues to be 4.3V. Hence, the output is a 1 bit. All these four cases satisfy the truth table of OR gate. A more input OR gate is obtained by using more diodes in the circuit. Analysing the truth table of OR gate, we learn that the output is 0 if both or all the inputs are 0, and the output is 1 if at least one of the inputs is 1.

Fig. 2.8 Realisation of OR gate using diodes

# Example 2.2

If the inputs A and B to OR gate are as shown in Fig. 2.9, trace the output Y.

Recall that the output of an OR gate is 1 if any of the input is 1, and the output is 0 if all the inputs are 0. With this understanding, the output comes out to be as shown in the trace for Y.

**Fig. 2.9**

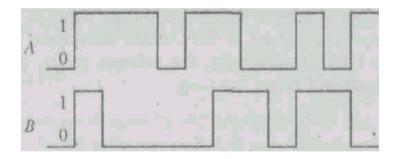

# SAQ 2

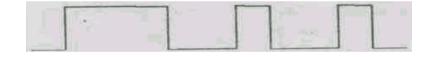

Trace the output of an OR gate if the inputs A and B are as shown in Fig. 2.10.

Fig. 2.10

#### **2.2.3 NOT** Gate

The NOT gate can be understood by considering the electrical circuit shown in Fig. 2.11, Let us assign a 0 bit to the event when bulb does not glow and 1 bit to the event when bulb glows, and a 0 bit to switch off and 1 bit to switch closed. In Fig. 2.11, when switch is closed, no current will pass through the bulb and the bulb will not glow. This is because the current always flows through the path of least resistance. Similarly, when the switch is open then the **whole** current will flow through the bulb making it glow.

Fig. 2.11 NOT gate using a switch

If input to the circuit is 1, the output is 0 and if the input is 0 then the output is 1. This is the NOT gate operation which is summarised in the truth table given in Table 2.3.

Table 11.3: Truth table for NOT gate

| A | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

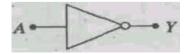

The NOT gate is also known as the INVERTER. It has only one input. Its symbol is given in Fig. 2.12. The input-output relationship is expressed as A = Y.

Fig. 2.12 Symbol of NOT gate

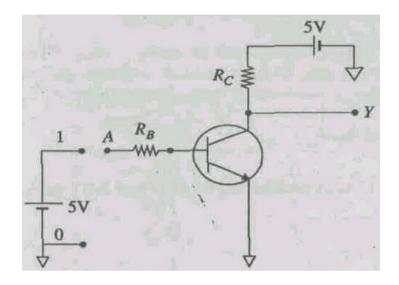

The NOT gate can be realised using the circuit given in Fig. 2.13. The circuit uses the cut-off and saturation modes of the transistor. When the

input to the circuit is a 0 bit, i.e. zero volt, no base current,  $I_B$ . flows. This means the collector current,  $I_C$  is zero. This is cut-off mode of the transistor.

Therefore, the output voltage is the bias voltage of 5V indicating the output to be a 1 bit. When the input to the circuit is a 1 bit, i.e. 5V, very large  $I_B$  flows resulting in very large  $I_C$ , in fact  $I_{C \text{ sat}}$ . This is the saturation mode of the transistor. This indicates that most of the bias voltage is dropped across  $R_C$ , with output to be a 0 bit.

Fig. 2.13 Realisation of NOT gate using a transistor

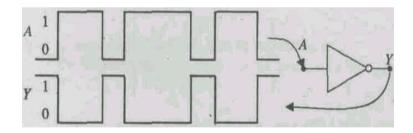

#### Example 2.3

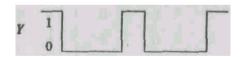

If the input A to NOT gate is as shown in Fig. 2.14, trace the output Y.

Fig. 2.14

#### **Solution**

Recall that the output of a NOT gate is 1 if the input is 0, and the output is 0 if the input is 1. With this understanding, the output comes out to be as shown in the trace for Y in Fig. 2.14.

### SAQ3

Trace the output of a NOT gate if the input is as shown in Fig. 2.15.

Fig. 11.15

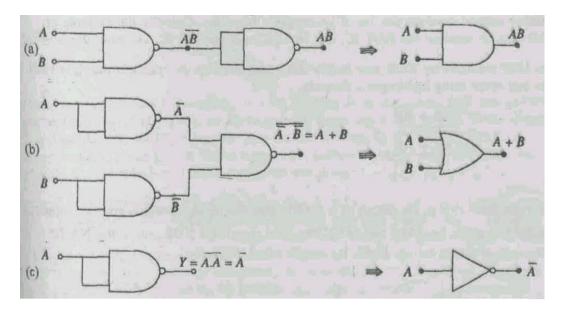

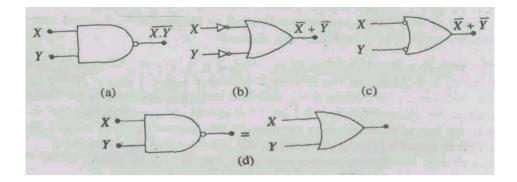

### 2.2.4 Combination of Logic Gates

The AND, OR and NOT gates are the fundamental gates for all digital circuits. These gates can be combined with each other for a particular application. However, two types of combinations are very important as you will learn now.

### (i) NAND Gate

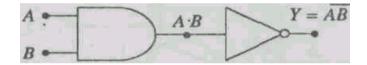

Fig. 2.16 Combination of AND and NOT gate

Fig. 2.17 Symbol of NAND gate

If the output of an AND gate is given to the input of a NOT gate, as shown in Fig. 2.16, the resulting circuit is known as NAND gate, the symbol of which is shown in Fig. 2.17. The truth table of this gate is obtained as follows:

| Α | В | Y' (AB) | Y |

|---|---|---------|---|

| 0 | 0 | 0       | 1 |

| 0 | 1 | 0       | 1 |

| 1 | 0 | 0       | 1 |

| 1 | 1 | 1       | 0 |

Thus the truth table of NAND gate is shown in Table 2.4.

Table 2.4: Truth table for NAND gate

| A | В | Y |  |

|---|---|---|--|

| 0 | 0 | 1 |  |

| 0 | 1 | 1 |  |

| 1 | 0 | 1 |  |

| 1 | 1 | 0 |  |

The input-output relationship of a NAND gate is expressed as A.B = Y. The NAND gate is known as the building block for the digital circuits because using NAND gates, one can obtain AND, OR and NOT gates. This aspect will be explained later.

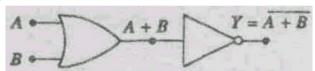

### (ii) NOR gate

Fig. 2.18 Combination of OR and NOT gate

Fig. 2.19 Symbol of NOR gate

If the output of an OR gate is given to the input of a NOT gate, as shown in Fig. 2.18, the resulting circuit is known as NOR gate, the symbol for which is shown in Fig. 2.19. The truth table of this gate is obtained as follows

| A | В | Y'(A + B) | Y |

|---|---|-----------|---|

| 0 | 0 | 0         | 1 |

| 0 | 1 | 1         | 0 |

| 1 | 0 | 1         | 0 |

| 1 | 1 | 1         | 0 |

The truth table of a NOR gate is shown in Table 2.5.

Table 2.5 Truth table for NOR gate

| A | В | Y |

|---|---|---|

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

The input-output relationship of a NOR gate is expressed as A + B = Y, The NOR is also known as the building block for the digital circuits because using NOR gates one can obtain AND, OR and NOT gates.

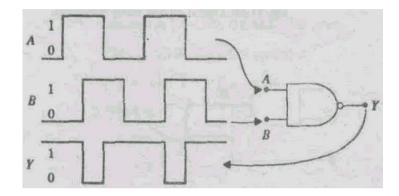

#### Example 11.4

If the inputs A and B to NAND gate are as shown in Fig. 2.20, trace the output Y.

Fig. 2.20

### Solution

Recall that the output of a NAND gate is 0 only when all the inputs are 1, and its output is 1 if any or all of the inputs is/are 0. With this understanding, the output comes out to be as shown in the trace for Y in Fig. 2.20.

## SAQ4

If the inputs A and B to a NOR gate are as shown in Fig. 2.21, trace its output Y. (Hint. Apply truth table 2.5).

Fig. 2.21

# 2.3 BOOLEAN ALGEBRA

In this section we shall learn about the Boolean algebra, which provides the methodology for reducing a complex digital circuit into a simple one. This methodology includes the following:

(1) The logic operations are written in the form of a Boolean expression.

(2) From the given truth table, a Boolean expression can be obtained which may not represent a simple circuit having minimum number of gates.

(3) The Boolean expression may then be simplified to get a digital circuit having minimum number of gates.

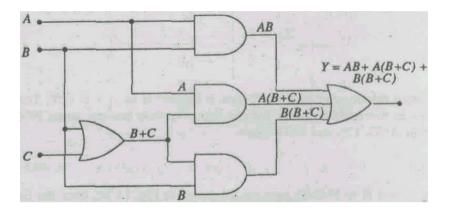

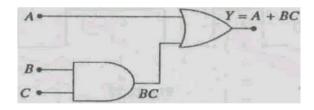

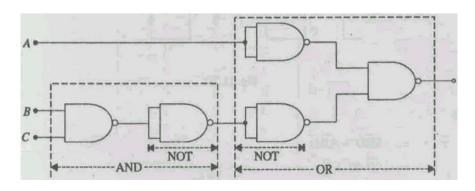

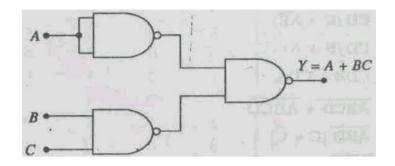

Consider the digital circuit given in Fig. 2.22. It has five logic gates of three types -

Fig. 2.22: Digital circuit using five gates

Fig. 2.23: Digital circuit having the same operation as that of the circuit given in Fig. 2.22

three 2-input AND gates, one 2-input OR gate and one 3-input OR gate. Its logic table is given in Table 2.6. This circuit can be reduced to the one shown in Fig. 2.23, which has only two logic gates and is considerably cheaper and simple. It fully satisfies the logic Table 2.6.

Table 2.6

| Α | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | I |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

1 1 1 I

The root of its initial assumptions, known as Boolean postulates, lies in the truth tables of the logic gates described in the previous section: Let us recall that the AND operation has been described by the sign of multiplication (.), that is, logical multiplication. Most often we do not use this sign (.), e.g. A.B = AB. Similarly the OR Operation has been described by the sign of addition (+), that is, logical addition. And the NOT operation has been described as a bar (-) over the variable, that is, logical inversion or complementation. These three operations are the basic Boolean operations based upon which we shall develop the Boolean algebra.

Since the number of bits used in binary system is only two, i.e. 0 and 1, there could be only four possible combination of inputs A and B to 2-input AND and OR gates, and two possible inputs to NOT gate. The logical tables of AND, OR and NOT gates are rewritten in Table 2.7.

Table 2.7: Truth tables of AND, OR and NOT gates

|   | AND |   |   |   | OR |   | N( | TC |

|---|-----|---|---|---|----|---|----|----|

| X | Y   | Z |   | X | Y  | Z | 0  | 1  |

| 0 | 0   | 0 | · | 0 | 0  | 0 | 1  | 0  |

| 0 | 1   | 0 |   | 0 | 1  | 0 |    |    |

| 1 | 0   | 0 |   | 1 | 0  | 0 |    |    |

| 1 | 1   | 1 |   | 1 | 1  | 1 |    |    |

These logic tables lead to ten postulates of the Boolean algebra, each of which describes the input-output relationship of the concerned logic gate in the form of Boolean expression and is one of the truth table entries for AND, OR, NOT functions. These are:

Table 2.8: Boolean expression for AND, OR and NOT gates

| AND operation   | OR operation | NOT operation |

|-----------------|--------------|---------------|

| $0 \cdot 0 = 0$ | 0 + 0 = 0    | 0 = 1         |

| $0 \cdot 1 = 0$ | 0 + 1 = 1    | 1 = 0         |

| $1 \cdot 0 = 0$ | 1 + 0 = 1    |               |

| $1 \cdot 1 = 1$ | 1 + 1 = 1    |               |

It is quite clear from these equations that all the four Boolean equations using AND operation satisfy the binary multiplication using bits 0 and 1. However, in the case of OR operation, the first three Boolean equation satisfy binary addition, but the last equation 1 + 1 = 1 does not. It is because in binary arithmetic 1 + 1 = 10. Despite this contradiction between Boolean and binary additions which will be settled later, the

Boolean operations are very helpful in digital circuits. The Table 2.8 will lead us to various Boolean theorems, which will be described in the following section.

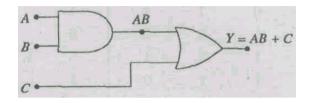

For the moment let us see how Boolean equations are written and used for a digital circuit. Consider the circuit of Fig. 2.24 in which A and B are the inputs to AND-gate

Fig. 2.24 Digital circuit for Y = A-B + C

while C is one of the inputs to OR gate. Another input to OR gate is the output of AND gate, i.e.,

AB. The output pf this combination is Y, which is

$$Y = (A \cdot B) + C = AB + C$$

Let us find Y if, say, A = 0, B = 1, and C = 1.

$$Y = 0 \cdot 1 + 1$$

From Table 2.8,  $0 \cdot 1 = 0$ , so

$$Y = 0 + 1$$

From Table 2.8.

$$0 + 1 = 1$$

Hence,

$$Y = 1$$

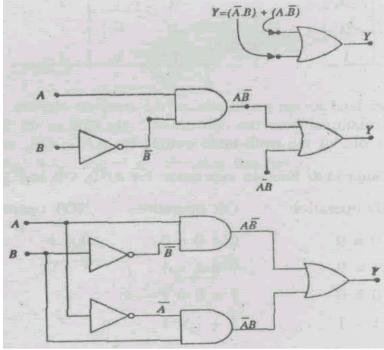

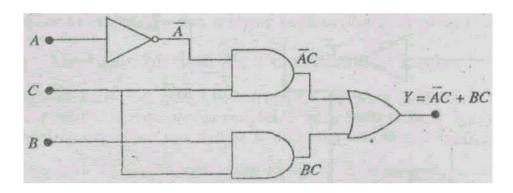

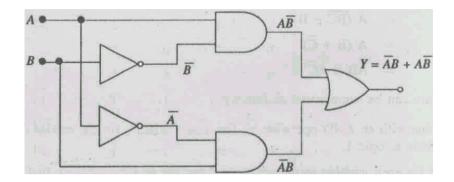

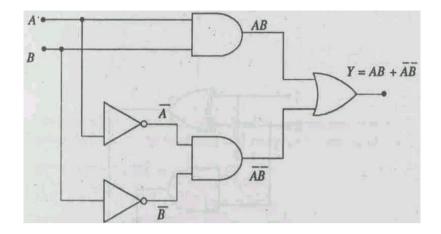

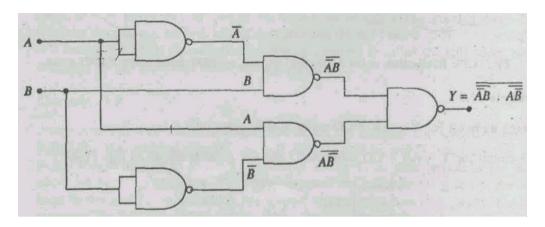

Let us now convert a given Boolean expression into a logic circuit. Say,  $Y = (\overline{A} \cdot B) + (A \cdot \overline{B})$ . The equation means that Y is the output of a 2-input OR gate the inputs to which are  $\overline{A} \cdot B$  and  $A \cdot \overline{B}$  which in turn are the outputs of two AND gates. The inputs to these AND gates are  $\overline{A}$  and B and A and  $\overline{B}$  respectively. The whole of this exercise is summarised in the Fig. 2.25.

Fig. 2.25 Conversion of a boolean expression  $Y = \overline{A}B + A\overline{B}$  a digital circuit

### 2.3.1 Boolean Theorems

Recalling Table 2.8 we can now write several identities or theorems which are used in Boolean algebra. It is also worthwhile to recall that

- A. (i) The output of an AND gate is 1 only when all the inputs are 1.

- (ii) The output of an AND gate is 0 when all or any of the inputs is 0.

- B. (i) The output of an OR gate is 0 when all the inputs are 0.

- (ii) The output of an OR gate is 1 when either of the inputs or all the inputs are 1.

- C. The output of a NOT gate is the inversion of its input.

From these conclusions and postulates, we derive the following properties or rules/law/ theorems: From AND function,

- 1.  $X \cdot 0 = 0$

- 2.  $0 \cdot X = 0$

- 3.  $X \cdot 1 = X$

4.

$$1 \cdot X = X$$

From OR functions,

5.

$$X + 0 = X$$

6.

$$0 + X = X$$

7.

$$X + 1 = 1$$

8.

$$1 + X = 1$$

Combination variable with itself or its complement,

9.

$$X \cdot X = X$$

10.

$$X \cdot \overline{X} = 0$$

11.

$$X + X = X$$

12.

$$X + \overline{X} = 1$$

From double complementation,

13.

$$\overline{\overline{X}} = X$$

Commutative laws for multiplication and addition. These laws show that the order in which two variables are ORed or ANDed together makes no difference.

14.

$$\mathbf{X} \cdot \mathbf{Y} = \mathbf{Y} \cdot \mathbf{X}$$

15.

$$X + Y = Y + X$$

Associative laws for addition and multiplication. These laws show that while ORing or ANDing several variables, it makes no difference in what order the variables are grouped.

16.

$$X + (Y + Z) \cdot (X + Y) + Z = X + Y + Z$$

17.

$$X(YZ) = (XY)Z = XYZ$$

Distributive laws.

18.

$$X \cdot (Y + Z) = (X \cdot Y) + (X \cdot Z)$$

19.

$$X + (Y \cdot Z) = (X + Y) \cdot (X + Z)$$

20.

$$(W + X) \cdot (Y + Z) = WY + XY + WZ + XZ$$

Note here that commutative, associative and distributive laws are similar to ordinary algebra.

Absorption laws. These have no counterpart in ordinary algebra.

21.

$$X + X \cdot Y = X$$

22.

$$X \cdot (X + Y) = X$$

23.

$$X + XY = X + Y$$

24.

$$X \cdot (\overline{X} + Y) = XY$$

De Morgan's theorems. The first theorem says that the complement of a sum is equal to the product of complements:

25.

$$\overline{X+Y} = \overline{X} + \overline{Y}$$

The second theorem says that the complement of a product is equal to the sum of the complements.

26.

$$\overline{X \cdot Y} = \overline{X} \cdot \overline{Y}$$

These theorems are valid even when the variables are expressions. There is no algebraic proof of these theorems. However, each theorem/law can be proved by putting the values (0 or 1) of variables and applying Boolean postulates given in Table 2.8.

#### 2.3.2 Algebraic Method for Combinational Logic

We have now known that a logic circuit can be expressed in the form of Boolean expression which, in turn, can be simplified using Boolean laws. We have also known that a Boolean expression can also be transformed into an equivalent logic circuit.

Before we learn the simplification method and other techniques, let us understand the meaning of combinational logic. Whenever a logic circuit is explicitly defined by its truth table to provide a fixed, invariant relationship between input and output, the circuit is called the combinational circuit. A combinational circuit does not have a memory. It always operates in accordance with its truth table regardless of any

prior input which may have been given to the circuit. This will be further understood after we have taken up some examples.

A Boolean expression can be simplified in either of the two forms - (a) Sum of Product (SOP), and (b) Product of Sum (POS). We shall limit ourselves to only SOP form, which is most commonly used. The object of simplification is to minimise the number of variables or occurrences of a variable in an expression. This means minimising operation symbols and hence the number of gates to be used in the circuit. Many a times we get more than one simplified form of an expression, each being equivalent in number of gates and variables to be used. In the final analysis, we shall use the Minimum Sum of Product (MSP) form which is written without brackets. Consider the reduced expression A (B + C) which is written in MSP form AB + AC. While the reduced expression requires one AND gate and one OR gate, the MSP expression requires one AND gates and one OR gate. Thus in this case MSP expression is not the simplest. The fundamental rule is that the expression must be (a) reduced as much as possible, and (b) written without brackets. For the simplification of Boolean expression, Boolean operations should be carried out in the following order:

- (1) Inversion of single variables.

- (2) All operations with brackets.

- (3) AND operations before OR operations.

- (4) OR operations.

- (5) If an expression is with a bar, then before inverting, perform all operations.

### Example 11.5

Find the MSP expression for

$$Y = (\overline{A} + \overline{B})\overline{C} + \overline{AB}$$

$$= (\overline{A} + \overline{B})\overline{C} + (\overline{A} + \overline{B})$$

Using De Morgan's theorem

Th. 26

$$= (\overline{A} + \overline{B})(\overline{C} + 1)$$

Taking  $(\overline{A} + \overline{B})$  common

$$= (\overline{A} + \overline{B}) \cdot 1$$

Using Th. 7

$$= (\overline{A} + \overline{B})$$

Using Th. 3

$$= MSP \text{ expression}$$

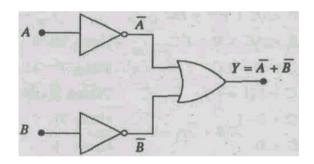

The logic circuits for the given and the MSP expressions are shown in Figs. 2.26 and 2.27 respectively.

Fig. 2.26 Digital circuit for  $Y = (\overline{A} + \overline{B})\overline{C} + \overline{AB}$

Fig. 2.27 Digital circuit for  $Y = \overline{A} + \overline{B}$

# Example 2.6

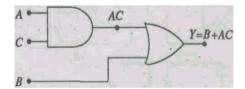

Find the MSP expression for  $Y = \overline{A}C + AB(\overline{B} + C)$

$$Y = \overline{A}C + AB(\overline{B} + C)$$

$$= \overline{A}C + AB\overline{B} + ABC$$

$$= \overline{A}C + A \cdot 0 + ABC \qquad \text{Using Th. 10}$$

$$= \overline{A}C + ABC \qquad \text{Using Th. 1}$$

$$= (\overline{A} + AB)C \qquad \text{Taking } C \text{ common}$$

$$= (\overline{A} + B)C \qquad \text{Using Th. 23}$$

$$= \overline{A}C + BC$$

$$= MSP \text{ expression}$$

Using Th. 10 Using Th. 1 Taking C common Using Th. ?\*

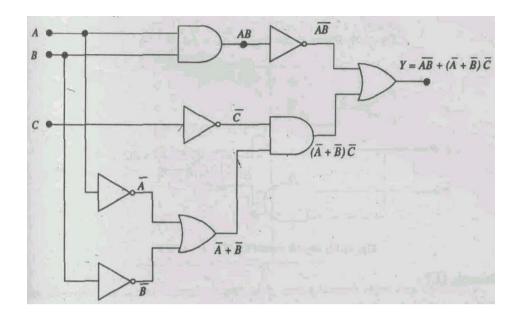

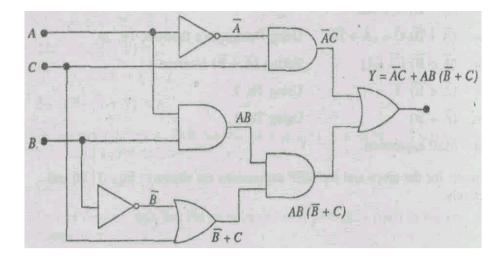

The logic circuits for the given expression and the MSP expressions are shown in Figs. 2.28 and 2.29 respectively.

Fig. 2.28 Digital circuit for  $Y = \overline{A}C + AB(\overline{B} + C)$

Fig. 2.29 Digital circuit for  $Y = \overline{A}C + BC$

# **Example 11.7**

Find the MSP expression for

```

Y

= AB + A (B + C) + B (3 + C)

= AB + AB + AC + BB + BC

Using Th. 9

= AB + AB + AC + B + BC

= AB + AC + B + BC

Using Th. 11

Taking B common

= AB + AC + B(1 + C)

= AB + AC + B \cdot 1

Using Th. 8

= AB + AC + B

Using Th. 3

= (A + 1) B + AC

= 1 \cdot B + AC

Using Th. 7

= B + AC

Using Th. 4

= MSP expression

```

The logic circuits for the given expression and the MSP expressions are shown in Figs. 2.22 and 2.23 respectively.

#### SAQ5

Find the MSP expression for  $Y = A\overline{B}\overline{C} + AB\overline{C} + ABC$ .

### 11.3.3 Obtaining a Truth Table from a Boolean Expression

A simple method of obtaining the truth table from a Boolean expression has already been mentioned. That is, substitute the values of variables in each possible combinations of values in the expression. Perform all the logic operations and get the result for each combination. For example,

$$Y = AB + A(B+C) + B(B+C)$$

In this expression, say, A = 1, B = 0, and C = 0, then

$$Y = 1 \cdot 0 + 1 \cdot (0 + 0) + 0 (0 + 0)$$

$$= 0 + 1 \cdot 0 + 0 \cdot 0$$

$$= 0 + 0 + 0$$

$$= 0$$

Similarly, find Y for all combinations of values for A, B, and C, and complete the truth table which is given in Table 11.9.

**Table 2.9: Truth table for** Y = AB + A(B + C) + B(B + C)

| A | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

The alternative method of obtaining a truth table from a Boolean expression involves reasoning. Ask yourself:

When shall the output of the expression be 1. Consider the expression

$$Y = A\overline{C} + BC = MSP$$

expression

This expression is 1 so long as either  $A\overline{C}$  or BC is 1. Therefore, put Y = 1 for all entries of  $A\overline{C} = 1$  (i.e., entries 5 and 7). Then put Y = 1 for all entries of BC = 1 (i.e., entries 4 and 8). Now, Y for all other entries is 0. Table 2.10 is thus the truth table for the given expression.

**Table 2.10: Truth table for**  $Y = A\overline{C} + BC$

|    | A | В | C | Y |

|----|---|---|---|---|

| 1. | 0 | 0 | 0 | 0 |

| 2. | 0 | 0 | 1 | 0 |

| 3. | 0 | 1 | 0 | 0                                           |

|----|---|---|---|---------------------------------------------|

| 4. | 0 | 1 | 1 | 1                                           |

| 5. | 1 | 0 | 0 | 1                                           |

| 6. | 1 | 0 | 1 | 0                                           |

| 7. | 1 | 1 | 0 | $\begin{bmatrix} 0 \\ 1 \\ 1 \end{bmatrix}$ |

| 8. | 1 | 1 | 1 | 1                                           |

Hence, it is better to use the method of reasoning for obtaining the truth table. This method involves just two steps:

- (1) Obtain the MSP form of the given Boolean expression, and

- (2) Reason out which of the truth table entries should be 1 for each product in MSP form.

### Example 11.8

Obtain the truth table for the Boolean expression Y = A + AB + BCD.

$$Y = A + AB + BCD$$

$$= A (1 + B) + BCD$$

$$= A \cdot 1 + BCD$$

$$= A + BCD$$

$$= MSP expression$$

Reasoning out we find that Y = 1 whenever A = 1 or the product BCD = 1. Therefore, in the truth table for this expression, put Y = 1 for all entries of A = 1, (i.e., entries 9 to 16) and put Y = 1 for all entries of product BCD = 1 (i.e. entries 8 and 16). For all other entries put Y = 0 (i.e. entries 1 to 7). The complete truth table is given in Table 2.11.

**Table 2.11: Truth table for** Y = A + AB + BCD

|     | A | В | C | D | Y |  |

|-----|---|---|---|---|---|--|

| 1.  | 0 | 0 | 0 | 0 | 0 |  |

| 2.  | 0 | 0 | 0 | 1 | 0 |  |

| 3.  | 0 | 0 | 1 | 0 | 0 |  |

| 4.  | 0 | 0 | 1 | 1 | 0 |  |

| 5.  | 0 | 1 | 0 | 0 | 0 |  |

| 6.  | 0 | 1 | 0 | I | 0 |  |

| 7.  | 0 | 1 | 1 | 0 | 0 |  |

| 8.  | 0 | 1 | 1 | 1 | 1 |  |

| 9.  | 1 | 0 | 0 | 0 | 1 |  |

| 10. | 1 | 0 | 0 | 1 | 1 |  |

| 11. | 1 | 0 | 1 | 0 | 1 |  |

| 12. | 1 | 0 | I | 1 | 1 |  |

| 13. | 1 | 1 | 0 | 0 | 1 |  |

| 14. | 1 | 1 | 0 | 1 | 1 |  |

| 15. | 1 | 1 | 1 | 0 | 1 |  |

| 16. | 1 | 1 | 1 | 1 | 1 |  |

#### **SAQ 6**

Obtain the truth table for Y = AB + BC + CA

# 2.3.4 Obtaining a Boolean Expression from a Truth Table

Consider the truth table given in Table 2.12.

Table 2.12: Given truth table

|    | A | В | C | Y                                      |

|----|---|---|---|----------------------------------------|

| 1. | 0 | 0 | 0 | 0                                      |

| 2. | 0 | 0 | 1 | $\begin{bmatrix} 0 \\ 0 \end{bmatrix}$ |

| 3. | 0 | 1 | 0 | 0                                      |

| 4. | 0 | 1 | i | 0                                      |

| 5. | 1 | 0 | 0 | 1                                      |

| 6. | 1 | 0 | 1 | 0                                      |

| 7. | 1 | 1 | 0 | 1                                      |

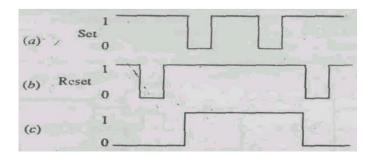

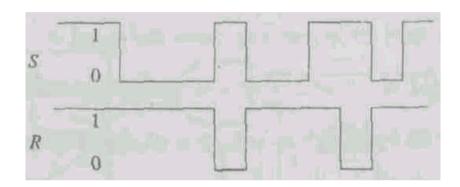

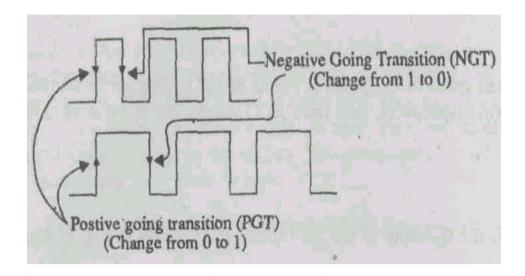

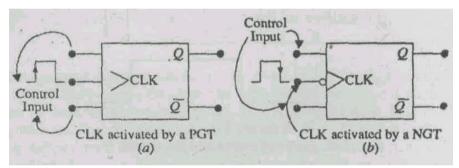

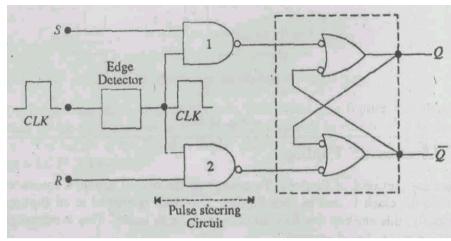

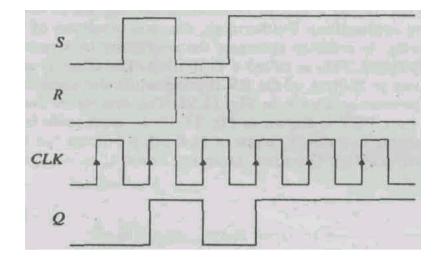

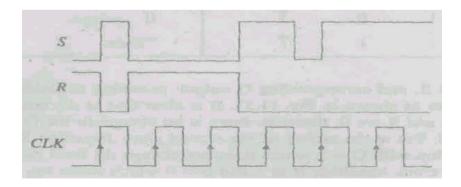

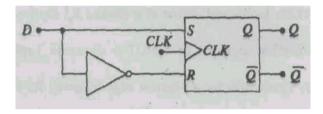

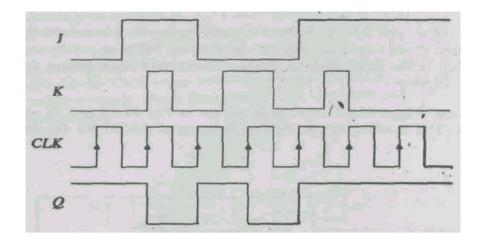

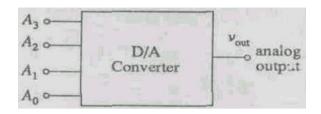

| 8. | 1 | 1 | 1 | 1                                      |